# Universidade Federal de Campina Grande Departamento de Sistemas e Computação Curso de Bacharelado em Ciência da Computação

# Organização e Arquitetura de Computadores I

# Organização Básica de Computadores (Exercícios Resolvidos, Parte II)

Profa Joseana Macêdo Fechine Régis de Araújo joseana@computacao.ufcg.edu.br

Carga Horária: 60 horas

- 1. Relacione a coluna da esquerda com a coluna da direita.

- (I) Multicore

- (A) Múltiplos pipelines que operam em paralelo.

- (II) Superpipeline (B) Execução de instruções fora de ordem em um pipeline.

- (III) Superescalar (C) Pipelines com grande número de estágios.

- (IV) Pipeline dinâmico (D) Múltiplos processadores compartilhando um espaço de endereços.

- (V) Multiprocessadores (E) Múltiplos processadores em um único encapsulamento.

Assinale a alternativa que contém a associação correta.

- a) I-B, II-A, III-C, IV-E, V-D.

- b) I-C, II-A, III-B, IV-D, V-E.

- c) I-D, II-E, III-B, IV-A, V-C.

- d) I-E, II-C, III-A, IV-B, V-D.

- e) I-E, II-C, III-A, IV-D, V-B.

- 1. Relacione a coluna da esquerda com a coluna da direita.

- (I) Multicore

- (A) Múltiplos pipelines que operam em paralelo.

- (II) Superpipeline (B) Execução de instruções fora de ordem em um pipeline.

- (III) Superescalar (C) Pipelines com grande número de estágios.

- (IV) Pipeline dinâmico (D) Múltiplos processadores compartilhando um espaço de endereços.

- (V) Multiprocessadores (E) Múltiplos processadores em um único encapsulamento.

Assinale a alternativa que contém a associação correta.

- a) I-B, II-A, III-C, IV-E, V-D.

- b) I-C, II-A, III-B, IV-D, V-E.

- c) I-D, II-E, III-B, IV-A, V-C.

- d) I-E, II-C, III-A, IV-B, V-D.

- e) I-E, II-C, III-A, IV-D, V-B.

2. A teoria da computabilidade, em conjunto com a álgebra booleana, garante que é possível construir um processador com um conjunto de instruções unitário que possua capacidade de resolver qualquer problema solúvel. Suponha que exista uma organização de computador convencional, dotada de um processador de uma instrução, memória e periféricos de entrada e saída.

Com relação à instrução única que o processador executa, considere as afirmativas a seguir.

- 1. Deve obrigatoriamente fazer acesso a um dispositivo de entrada e saída.

- II. Deve obrigatoriamente ler e escrever na memória principal do processador.

- III.Deve obrigatoriamente calcular uma soma de produtos de literais booleanos.

- IV.Deve obrigatoriamente realizar um teste, e sua ação deve ser condicionada ao resultado deste teste.

Assinale a alternativa correta.

- a) Somente as afirmativas I e II são corretas.

- b) Somente as afirmativas II e IV são corretas.

- c) Somente as afirmativas III e IV são corretas.

- d) Somente as afirmativas I, II e III são corretas.

- e) Somente as afirmativas I, III e IV são corretas.

2. A teoria da computabilidade, em conjunto com a álgebra booleana, garante que é possível construir um processador com um conjunto de instruções unitário que possua capacidade de resolver qualquer problema solúvel. Suponha que exista uma organização de computador convencional, dotada de um processador de uma instrução, memória e periféricos de entrada e saída.

Com relação à instrução única que o processador executa, considere as afirmativas a seguir.

- 1. Deve obrigatoriamente fazer acesso a um dispositivo de entrada e saída.

- II. Deve obrigatoriamente ler e escrever na memória principal do processador.

- III.Deve obrigatoriamente calcular uma soma de produtos de literais booleanos.

- IV.Deve obrigatoriamente realizar um teste, e sua ação deve ser condicionada ao resultado deste teste.

Assinale a alternativa correta.

- a) Somente as afirmativas I e II são corretas.

- b) Somente as afirmativas II e IV são corretas.

- c) Somente as afirmativas III e IV são corretas.

- d) Somente as afirmativas I, II e III são corretas.

- e) Somente as afirmativas I, III e IV são corretas.

Um programa X que executa 200 instruções é usado para comparar o desempenho das organizações. Das 200 instruções, apenas 40% fazem acesso à memória, enquanto as demais operam apenas sobre registradores internos da organização. Assuma que o programa não apresenta nenhum conflito de dados ou de controle entre instruções que podem estar simultaneamente dentro do pipeline da segunda organização.

Assim, o tempo de execução do programa X nas organizações monociclo e pipeline é, respectivamente:

- a) 2.000 nanossegundos e 510 nanossegundos.

- b) 2.000 nanossegundos e 500 nanossegundos.

- c) 2.000 nanossegundos e 2.300 nanossegundos.

- d) 2.300 nanossegundos e 500 nanossegundos.

- e) 2.300 nanossegundos e 510 nanossegundos.

Um programa X que executa 200 instruções é usado para comparar o desempenho das organizações. Das 200 instruções, apenas 40% fazem acesso à memória, enquanto as demais operam apenas sobre registradores internos da organização. Assuma que o programa não apresenta nenhum conflito de dados ou de controle entre instruções que podem estar simultaneamente dentro do pipeline da segunda organização.

Assim, o tempo de execução do programa X nas organizações monociclo e pipeline é, respectivamente:

- a) 2.000 nanossegundos e 510 nanossegundos.

- b) 2.000 nanossegundos e 500 nanossegundos.

- c) 2.000 nanossegundos e 2.300 nanossegundos.

- d) 2.300 nanossegundos e 500 nanossegundos.

- e) 2.300 nanossegundos e 510 nanossegundos.

#### **Observações:**

Organização da máquina Versão 1

Período para execução de uma instrução

$[1/(100 \times 10^6)] s = 10 \text{ ns}$

Período para execução de 200 instruções

$200 \times 10 \text{ ns} = 2.000 \text{ ns}$

### Pipeline:

#### **Observações:**

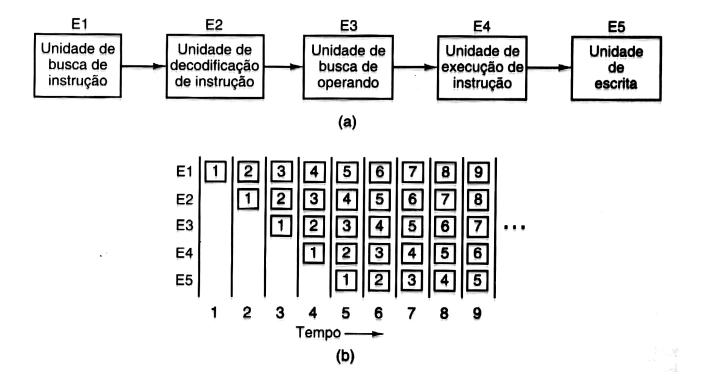

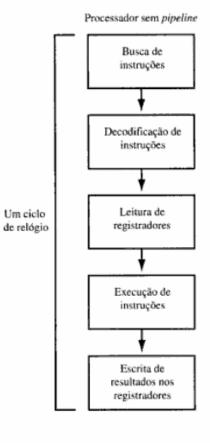

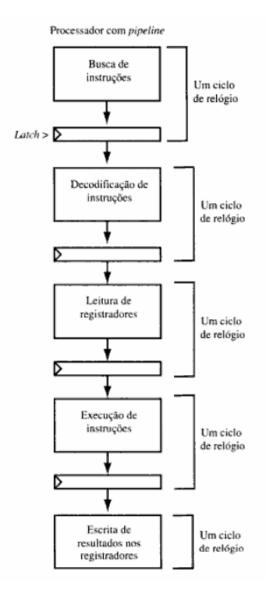

Organização da máquina segundo uma estrutura de um pipeline com 5 estágios, considerando cada módulo como indivisível e sem atraso.

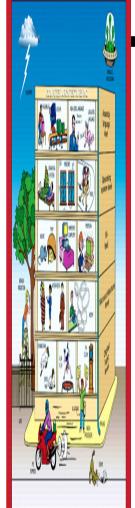

Período do *pipeline*  $[1/(400 \times 10^6)]$  s = 2,5 ns Período para execução de 200 instruções (Observar o princípio da Figura 1)

- 40% fazem acesso à memória (80 instruções utilizam 5 estágios)

- 60% operam apenas sobre registradores internos da organização (120 instruções – utilizam 4 estágios).

#### Observações:

Organização da máquina segundo uma estrutura de um *pipeline* com 5 estágios, considerando cada módulo como indivisível e sem atraso.

Estágio 1: 200 períodos de clock (200 instruções)

Estágio 2: tem início no segundo período de clock para a instrução

1. Logo, para execução deste estágio em todas as instruções, temse mais um período de clock em relação ao estágio anterior;

Estágio 3: ....

Importante: 40% e 60% (descritos anteriormente) estarão inseridos no tempo necessários à execução do pior caso (5 estágios).

Logo, o período para execução das 200 instruções é:

$(200 + 1 + 1 + 1 + 1) \times 2.5 \text{ ns} = 510 \text{ ns}$

4. Um processador tem um ciclo de operação igual a 20ns. Ele gasta dois ciclos para fazer a busca de uma instrução, um ciclo para decodificar cada instrução, dois ciclos para buscar os operandos necessários e três ciclos para executar a instrução e armazenar o resultado correspondente em algum registrador.

Se a organização desta máquina for estritamente sequencial, qual será o período de execução de uma instrução? Se utilizarmos latches de 2ns de atraso e considerarmos cada módulo como indivisível, qual será o período do pipeline se a máquina for organizada segundo uma estrutura de quatro estágios?

- a) Respectivamente 20ns e 22ns.

- b) Respectivamente 20ns e 42ns.

- c) Respectivamente 20ns e 62ns.

- d) Respectivamente 160ns e 42ns.

- e) Respectivamente 160ns e 62ns.

4. Um processador tem um ciclo de operação igual a 20ns. Ele gasta dois ciclos para fazer a busca de uma instrução, um ciclo para decodificar cada instrução, dois ciclos para buscar os operandos necessários e três ciclos para executar a instrução e armazenar o resultado correspondente em algum registrador.

Se a organização desta máquina for estritamente sequencial, qual será o período de execução de uma instrução? Se utilizarmos latches de 2ns de atraso e considerarmos cada módulo como indivisível, qual será o período do pipeline se a máquina for organizada segundo uma estrutura de quatro estágios?

- a) Respectivamente 20ns e 22ns.

- b) Respectivamente 20ns e 42ns.

- c) Respectivamente 20ns e 62ns.

- d) Respectivamente 160ns e 42ns.

- e) Respectivamente 160ns e 62ns.

#### Observações:

- Um sinal de relógio comum sincroniza os latches da pipeline em cada estágio, e dessa forma todos os latches guardam os dados produzidos de cada estágio ao mesmo tempo. O relógio vai assim "bombeando" as instruções ao longo do pipeline.

- No início de um período de relógio, ou ciclo de relógio, os dados e controle das instruções parcialmente processadas são mantidos num pipeline latch até ao final desse ciclo.

#### Observações:

Exemplo de processador sem pipeline e com pipeline.

#### Observações:

O tempo de ciclo  $\tau$  de um *pipeline* de instrução é o tempo requerido para avançar um conjunto de instruções de um estágio. O tempo de ciclo pode ser determinado da seguinte forma:

$$\tau = \max(\tau_i) + d = \tau_m + d, 1 \le i \le k$$

em que:

$\tau_m$  = atraso máximo de estágio

k = número de estágios do pipeline de instrução

d = tempo necessário para propagar sinais e dados de um estágio para o próximo

Em geral, d é equivalente ao pulso de um relógio e  $\tau m >> d$ .

#### Observações:

Informações fornecidas na questão:

- 1 ciclo de operação = 20 ns;

- 2 ciclos para busca da instrução;

- 1 ciclo para decodificação da instrução;

- 2 ciclos para busca dos operandos necessários;

- 3 ciclos para execução da instrução e armazenamento do resultado correspondente em algum registrador.

### **Observações:**

Organização da máquina estritamente sequencial

Período de execução de uma instrução

$$(2x20 + 1x20 + 2x20 + 3x20)$$

ns =

$$(40 + 20 + 40 + 60) =$$

**160 ns**

#### **Observações:**

Organização da máquina segundo uma estrutura de um *pipeline* com quatro estágios, considerando cada módulo como indivisível e a utilização de *latches* de 2ns de atraso.

Período do *pipeline* = 62 ns

Como foi obtido este valor?